Die-to-die variations (also referred to as global or interdie variations) affect all the devices on the same die in the same way. For instance, they cause the CD of all devices on the same chip to …

Static timing analysis - Wikipedia

Each corner represents a specific combination of PVT parameters. STA tools evaluate timing across multiple corners to guarantee correct functionality under all expected operating conditions.

Now, let’s formulate a new true Corner Definition: Corner is a point in the PVT/RC/+ space where cell/net delays have extreme (and optionally nominal) values—all cell delays are the max …

Achieving Successful Multi-Die Signoff - Semiconductor Engineering

Dec 19, 2024 · Multi-die STA faces challenges with worst-case and best-case timing paths crossing dies at different process, voltage, and temperature (PVT) corners, potentially leading …

Process variation can be briefly categorized into chip-to-chip (die-to-die) variation and on-chip variation (OCV). In the traditional static timing analysis, the chip-to-chip variation effect is …

ASIC design margin methodology - IEEE Xplore

On-chip variation (OCV) analysis is one of the design issues faced by STA owners in advance technology node. In the past, typical OCV analysis assumed the worst process variation at …

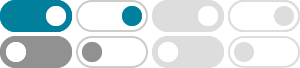

Operating conditions What is Static Timing Analysis? Static Timing Analysis (STA) is a critical method for. verifying the timing performance of a digital design. It differs from timing …

Instead, designers employ corner analysis, where STA runs are performed at a number of PVT settings, referred to as corners. By doing this, it becomes possible to capture a circuit’s worst …

It accounts for intra-die process variations and hence eliminates the pessimism in deterministic timing analysis, based on case files. It is a more accurate measure of which paths are critical …

There is yet another challenge in multi-die STA: worst-case and best-case timing paths may cross between two dies at very different process, voltage, and temperature (PVT) corners.